Introduction to Design Verification

The course start date TBC

Course Objectives

Introduction to Semiconductor Design Verification (DV)

By the end of the course, participants should be able to

1. Describe the best-practice DV strategies applied currently to semiconductor digital designs

2. Understand the main methodologies, tools and languages used in those best-practice DV strategies

3. Apply those DV methodologies, tools and languages to basic digital designs at IP and subsystem level

4. Analyse a “real” semiconductor digital design (IP and subsystem) and suggest an appropriate DV strategy

5. Understand best-practice DV so they can discuss DV topics confidently with colleagues

6. Have sufficient understanding of DV tools and methodologies to contribute effectively to real projects

For more information on the course, check out the video here: https://www.youtube.com/watch?v=Y5E3YDXMQgI

Course overview and structure

The course runs for 5 weeks with the following main activities. Details are given using the links.

1. 7 online one-hour lectures covering the major DV topics (details)

• Supported by exercises (using both SystemVerilog and VHDL) (details)

2. 6 Practical sessions

3. 2 online one-hour lectures covering debug (details)

• Supported by exercises (using both SystemVerilog and VHDL) (details)

4. A large collection of design and verification examples and exercises graded as different levels of difficulty and complexity

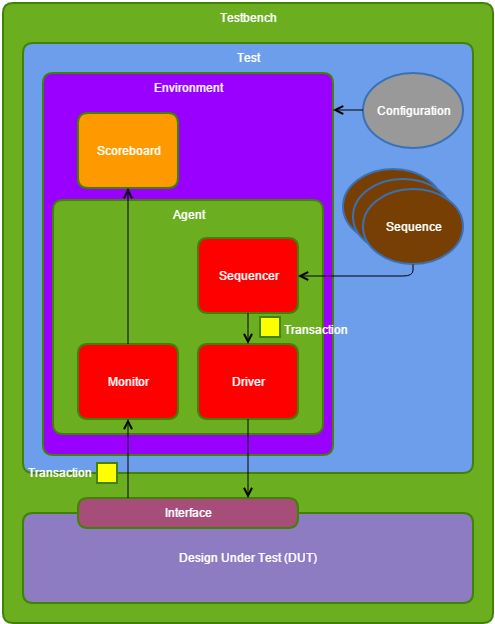

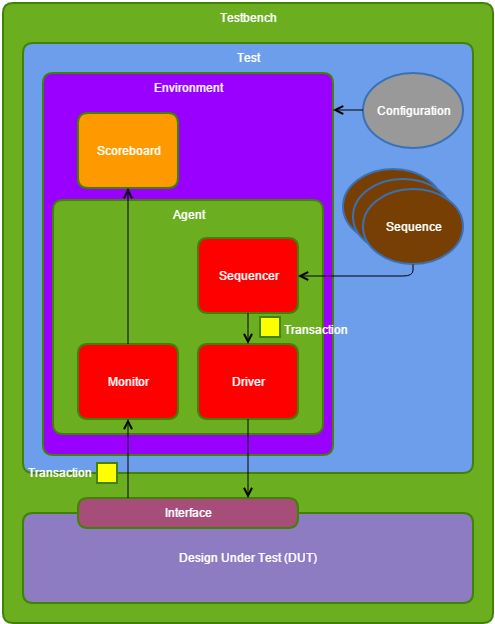

5. A number of pre-recorded videos covering: running tools; overview of design and verification languages; introduction to writing designs; overview of test bench languages, methodologies and structures;

6. Access to tools in the cloud for running online exercises (details)

• There will also be a non-cloud option that allows participants to download the exercises and run them on their own machine with their own licenses.

7. Access to online Cadence courses using the latest languages, tools and techniques (limited access) (details)

Note that participants will get additional support outside the lectures and exercises as needed.

Preparatory and follow-on reading will be suggested but neither are obligatory. There is no (summative or formative) assessment

Pre-requisites

There are no pre-requisites, although some experience of programming (preferably with an Object-Oriented language) would be useful. The course is suitable for a wide range of people working in semiconductor design and development, especially recent graduates.

Step 1 – Registration

Register / make an enquiry

Want to register or simply find out more? Complete the form below.

Step 2 – Secure Payment

If you are ready to make payment now, select the correct button below to make secure payment via credit card using the Sagepay system. Prices are based on whether your company is a TechWorks member organisation or a non-member. If you would like to check if you are a member, click HERE.

Course Start Date

The TechWorks Academy present the course to introduce participants to DV.

The course starts in September with dates to be confirmed. We also welcome new additions such as the Feature Extraction and Automation/AI Course. The new RiscV Verification course to be added soon.

Target Audience

1. University students going on or started a placement at a semiconductor design company

2. Design engineers wanting to learn more about verification and/or how to write re-usable verification IP

3. University graduates starting or started work at a semiconductor design company

4. Engineers wanting to transition their career to or are just curious about DV

5. Managers wanting some understanding of the topic

Delegate Pricing

- Member = £1200 per delegate

Valid to any TechWorks community member*

- Non-member = £1500 per delegate

Testimonial

The flexible delivery and timing of the course allowed participants to continue working on their own assigned projects during the training. We did not have to assign internal senior engineers to support the upskilling of these engineers.

The course was delivered by a very senior presenter with over 30 years’ experience in Design Verification. He was able to provide valuable insights into the practicalities of verifying real designs and was very responsive to participant questions, taking time outside of the online sessions to give individual support.

After the 1st run and full delivery of the course, the organiser took extensive feedback from all participants which has now been incorporated into the next course. The next course will start on February 7th and we have already registered 8 participants for this.

Pete Leonard, Electronics Design Manager, Group Engineering, Renishaw

Introduction to Design Verification (DV)

The TechWorks Academy present the course to introduce participants to DV. The course starts on Tuesday 7th Feb 2023 and runs for 5 weeks on every Tuesday, Wednesday and Thursday 4pm to 5pm

Course overview and structure

The course runs for 5 weeks with the following main activities. Details are given using the links.

1. 7 online one-hour lectures covering the major DV topics (details)

• Supported by exercises (using both SystemVerilog and VHDL) (details)

2. 6 Practical sessions

3. 2 online one-hour lectures covering debug (details)

• Supported by exercises (using both SystemVerilog and VHDL) (details)

4. A large collection of design and verification examples and exercises graded as different levels of difficulty and complexity

5. A number of pre-recorded videos covering: running tools; overview of design and verification languages; introduction to writing designs; overview of test bench languages, methodologies and structures;

6. Access to tools in the cloud for running online exercises (details)

• There will also be a non-cloud option that allows participants to download the exercises and run them on their own machine with their own licenses.

7. Access to online Cadence courses using the latest languages, tools and techniques (limited access) (details)

Note that participants will get additional support outside the lectures and exercises as needed.

Preparatory and follow-on reading will be suggested but neither are obligatory. There is no (summative or formative) assessment

Register Interest

Want to find out more? Complete the form and we will contact you with more details

Course Objectives

By the end of the course, participants should be able to

1. Describe the best-practice DV strategies applied currently to semiconductor digital designs

2. Understand the main methodologies, tools and languages used in those best-practice DV strategies

3. Apply those DV methodologies, tools and languages to basic digital designs at IP and subsystem level

4. Analyse a “real” semiconductor digital design (IP and subsystem) and suggest an appropriate DV strategy

5. Understand best-practice DV so they can discuss DV topics confidently with colleagues

6. Have sufficient understanding of DV tools and methodologies to contribute effectively to real projects

Pre-requisites

There are no pre-requisites, although some experience of programming (preferably with an Object-Oriented language) would be useful. The course is suitable for a wide range of people working in semiconductor design and development, especially recent graduates.

Target Audience

1. University students going on or started a placement at a semiconductor design company

2. Design engineers wanting to learn more about verification and/or how to write re-usable verification IP

3. University graduates starting or started work at a semiconductor design company

4. Engineers wanting to transition their career to or are just curious about DV

5. Managers wanting some understanding of the topic

Testimonial

The flexible delivery and timing of the course allowed participants to continue working on their own assigned projects during the training. We did not have to assign internal senior engineers to support the upskilling of these engineers.

The course was delivered by a very senior presenter with over 30 years’ experience in Design Verification. He was able to provide valuable insights into the practicalities of verifying real designs and was very responsive to participant questions, taking time outside of the online sessions to give individual support.

After the 1st run and full delivery of the course, the organiser took extensive feedback from all participants which has now been incorporated into the next course. The next course will start on February 7th and we have already registered 8 participants for this.

Pete Leonard, Electronics Design Manager, Group Engineering, Renishaw